Translation Barrier Instruction

Invented by Gonion; Jeff

Modern computer chips are complicated. They need to run programs quickly and safely, often doing many things at once. The patent application we are exploring introduces a new tool for chip designers: the translation barrier instruction. This instruction helps computer chips keep different tasks in order when the chip is translating addresses, which is key for running programs smoothly and avoiding mistakes. In this article, you’ll learn why this invention matters, how it fits into the world of computer chips, what older solutions existed, and what’s new and special about this patent.

Background and Market Context

To understand this invention, let’s first talk about how computer chips work today and what problems they face.

Most modern computers—from desktops and laptops to phones and tablets—have chips called processors. These chips are like the brains of the device. They run programs by following instructions. But running programs isn’t as simple as doing one thing after another. To go faster, processors often do things out of order. If one instruction has to wait for something slow, like reading from memory, the processor can work on other instructions in the meantime. This is called out-of-order processing.

But there’s a catch. Programs use virtual addresses to talk about memory. The chip has to translate these to physical addresses—the real spots in memory where data is stored. This translation isn’t always instant and can get complicated, especially when programs move around in memory or when the rules about who can access what change.

Chips use special tools to help with address translation. They have things like translation tables and translation lookaside buffers (TLBs) that remember recent translations so they don’t have to do the work over and over. But sometimes, these translations need to change—maybe because a new program starts, or because the computer’s security settings change.

When these changes happen, it’s very important that the chip doesn’t get mixed up. If the chip uses an old translation when it should be using a new one, it could read or write the wrong data, or break security rules. This is especially tricky when the chip is running instructions out of order. Some instructions might be using old translations, while others are ready to use the new settings.

Before this invention, chips used barrier instructions to help keep things in order. A barrier instruction is like a stop sign. It tells the chip: “Wait here until everything before this is done.” But the old barriers had problems. They often made the chip throw away a lot of work and start over, which slowed everything down. They also sometimes stopped more things than necessary, hurting performance.

The market is hungry for faster, more efficient chips that can run many programs safely at once. Devices like phones, tablets, smart watches, and even cars and home appliances all need chips that are reliable but don’t waste power or time. Cloud servers, which run many programs for lots of people at once, also need chips to be efficient and secure. This means chip makers are always looking for better ways to handle address translations without slowing down or risking mistakes.

This is the world the translation barrier instruction enters—a world where speed, safety, and the ability to run many programs at once all matter. The new instruction aims to let chips keep things in order when updating address translations, without throwing away good work or slowing down more than needed.

Scientific Rationale and Prior Art

Let’s look closer at the science behind the invention and what solutions have come before.

At the heart of this invention is the problem of synchronization. Out-of-order processors can do many things at once, but sometimes, certain actions must be done in a strict order to avoid errors. Changing how addresses are translated is one of these times. If the chip lets new translations happen before it has finished all the old ones, things can go wrong.

Older chips solved this by using general barrier instructions. These instructions made the processor stop and wait until all earlier instructions were done. Sometimes, the chip would even flush its instruction pipeline (throw away all work in progress and start over). This made sure nothing happened out of order, but it wasted time. Imagine cleaning your whole room every time you wanted to put away one toy—safe, but not smart.

Some processors let speculative work happen. This means the chip might guess what will happen next and start working on it early. If the guess is right, things are faster. If not, the chip throws away the work. But with address translations, guessing can be dangerous. If the translation changes while the chip is speculating, it could remember the wrong result.

Prior art includes various types of barriers:

- Full memory barriers: These make the processor wait until all memory operations are done before moving on. They guarantee order but slow things down.

- Pipeline flushes: These clear out all instructions in progress. They are safe but waste a lot of work.

- Permission and translation checks: These make sure programs don’t access memory they shouldn’t. But they don’t always handle the timing of translation table changes well if instructions are running out of order.

Older barriers were big hammers—they stopped everything to be safe. This was okay when processors did things in order and worked on one program at a time. But now, chips are more advanced. They run many programs, do things out of order, and need to keep working as much as possible to save power and time.

The translation barrier instruction in this patent is a new tool. It is more specific. It only blocks address translations for instructions that come after the barrier. It does not flush the whole pipeline or stop every kind of work. It also makes sure that changes to system registers (the places the chip stores important settings) are done in the right order. And it handles speculative work by making sure that, if the chip guesses about a translation, it doesn’t remember the guess unless it’s safe.

This is a more surgical approach. It gives the chip a way to say, “Let’s pause just the things that could go wrong if done out of order, but let everything else continue.” This way, the chip is both safe and fast. It doesn’t throw away good work, and it doesn’t block things that don’t need to be blocked.

The invention stands apart from previous solutions by providing fine-grained control. It recognizes that not all instructions need to be stopped for a translation table update, just those that might be affected. It also allows some speculative work but ensures it won’t cause a problem. This is a step forward from the older, broader barriers that didn’t offer this level of control.

Invention Description and Key Innovations

Now, let’s explain how the translation barrier instruction works and what makes it special.

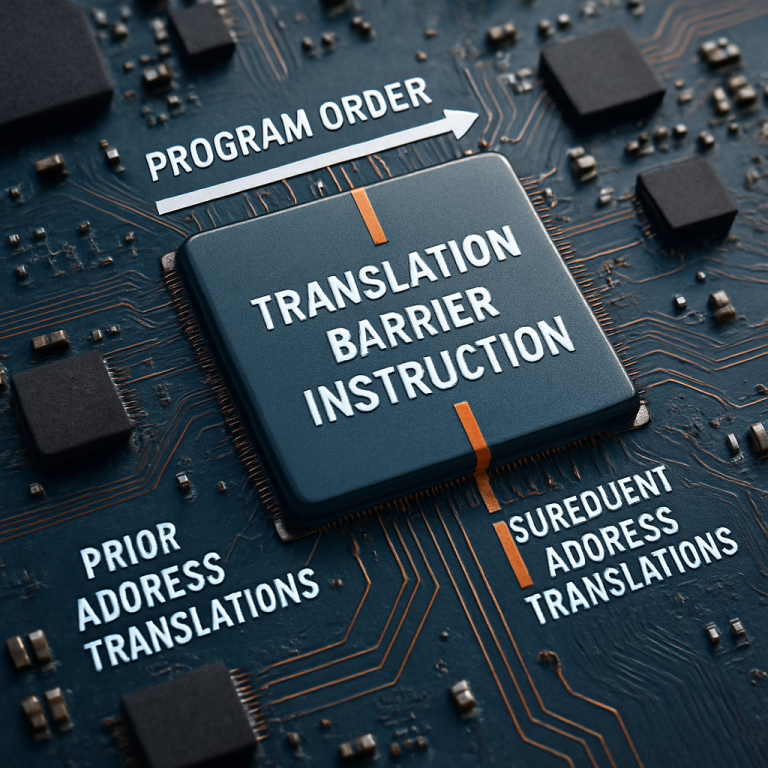

The invention is an instruction—a special command the processor can run—called a translation barrier instruction. When the processor sees this instruction, it follows some new rules to keep address translations in order.

Here’s what happens:

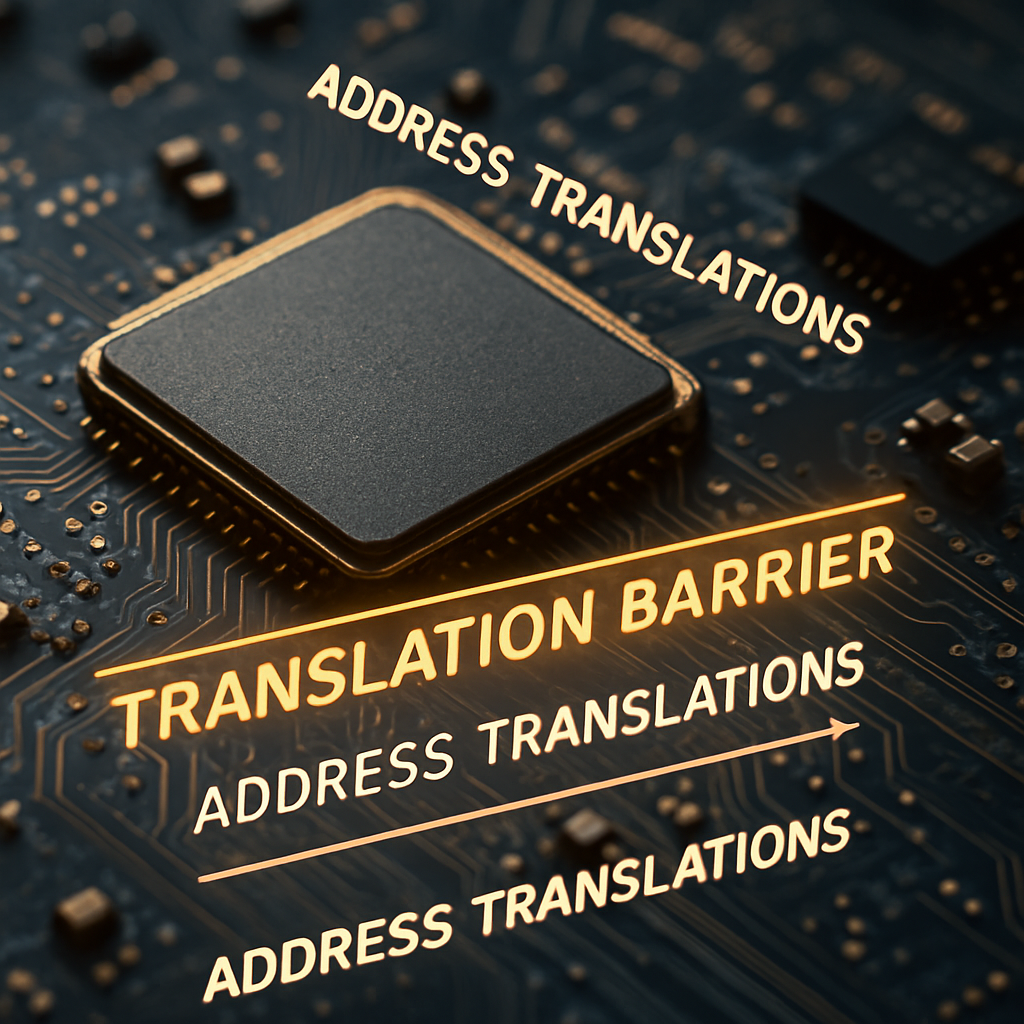

When the processor executes a translation barrier instruction, it looks at the “program order.” This is just the normal order in which the instructions were written, even if the chip is running some out of order. The translation barrier says, “Finish all address translations for instructions before me. Do not start address translations for instructions after me until I’m done.”

This means if there are still old translations happening when the barrier is reached, the chip waits for them to finish. But it doesn’t stop everything—just the translations that could be affected by changes in the translation tables or system registers. Other work, like math or logic on data already in registers, can keep going as long as it doesn’t need a new address translation.

Once all old translations are done, the chip allows changes to the translation tables or registers to happen. These could be things like updating which part of memory belongs to which program, or changing who has permission to access certain data.

For instructions after the barrier, the processor waits to start their address translations until the barrier is done. This keeps everything in the right order and stops mistakes where an instruction might use the wrong address translation.

The invention also covers changes to system registers. These are special places where the chip keeps important settings, like the base address of a translation table. The translation barrier can be set up to block changes to all system registers, or just those that affect translations or permissions. The barrier doesn’t finish until all register changes before it are done, and it stops register changes after it until it completes. This prevents a new setting from being used by an instruction that should still be using the old one.

Another key feature is how the invention handles speculative translation. If the processor starts a speculative translation for an instruction that comes after the barrier, the result won’t be cached in the TLB (the fast memory for translations) until the barrier is done. This means the chip won’t remember a wrong guess if the translation tables change during the barrier.

In some versions, if an instruction after the barrier needs a translation, the processor can “stall” (pause) just that instruction until the barrier is done, instead of stalling the whole processor. This is more efficient—other instructions that don’t need new translations can keep running. The chip can also decide not to issue new instructions that depend on translations after the barrier, further avoiding wasted work.

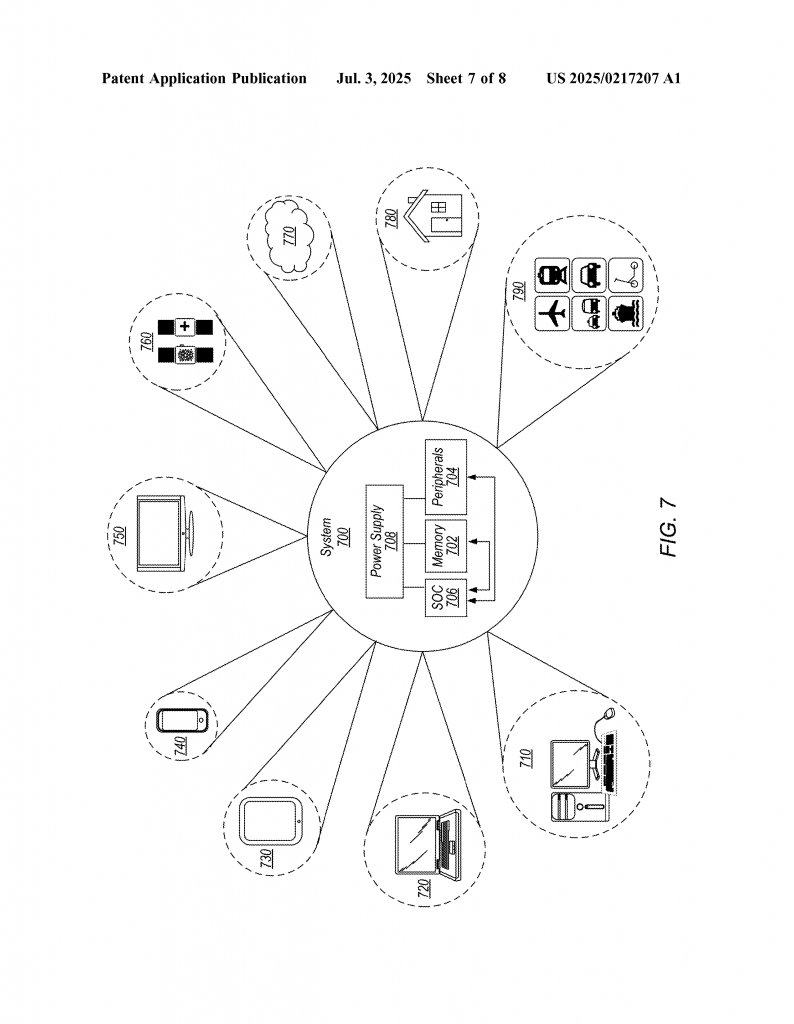

The invention can be used in many types of devices. It works in chips with one or many cores, in computers, phones, tablets, and even in smart home devices or cars. It can be part of a system-on-chip (SOC) or in a system with several chips working together.

In summary, the translation barrier instruction lets the processor:

- Finish all old address translations before starting new ones that could be affected by changes.

- Allow only the needed instructions to be paused, keeping the rest running for better speed.

- Handle changes to system registers in order, so no instruction uses the wrong settings.

- Block speculative translation results from being used if they might be wrong.

This leads to better performance, less wasted work, and safer, more reliable chips.

From an engineering standpoint, the patent introduces a smart mechanism that fits into the processor’s instruction pipeline. The pipeline can keep track of which instructions are older or younger than the barrier. It lets address translations and register changes finish in the right order, and controls when new translations can begin or be cached. The chip designer can decide how broad or narrow the barrier should be, depending on what system registers it covers.

The patent also covers the method for doing all this, not just the hardware. The method includes steps for when the barrier is issued, how it blocks translations and register changes, how it checks that older work is done, and how it lets things proceed once the barrier is finished. This gives both hardware and software designers a clear map for adding the translation barrier instruction to new chips.

Conclusion

The translation barrier instruction is an important step forward for processor design. It gives chips a way to keep address translations and system settings in the correct order without stopping more work than necessary. By being more precise and less wasteful than older barriers, it helps processors run faster and safer, making them better suited for today’s busy, multi-program world.

For chip makers, this means they can build processors that handle complex tasks and many programs at once, without risking mistakes in memory access. For users, it means devices that are faster, more reliable, and safer. This invention is a good example of how careful improvements in low-level chip design can make a big difference in the performance and trustworthiness of all kinds of technology, from phones to servers to cars.

Click here https://ppubs.uspto.gov/pubwebapp/ and search 20250217207.